# **Core Coprocessor Interface Specification**

Document Number: MD00068 Revision 1.16 August 20, 2004

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 2000-2004 MIPS Technologies Inc. All rights reserved.

Copyright © 2000-2004 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS, MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS-3D, MIPS16, MIPS16e, MIPS32, MIPS64, MIPS-Based, MIPSsim, MIPS Technologies logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 20Kc, 25Kf, 24K, 24Kc, 24Kf, R3000, R4000, R5000, ASMACRO, ATLAS, At The Core Of The User Experience., BusBridge, CorExtend, CoreFPGA, CoreLV, EC, FastMIPS, JALGO, MALTA, MDMX, MGB, MIPS RISC CERTIFIED POWER logo, PDTrace, the Pipeline, Pro Series, QuickMIPS, SEAD, SEAD-2, SmartMIPS, SOC-it, and YAMON are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

Template: S1.13, Built with tags: 2B

# Table of Contents

| Core Coprocessor Interface Specification          | 4  |

|---------------------------------------------------|----|

| 1 Introduction                                    |    |

| 2 Coprocessor Instructions                        | 5  |

| 3 Signal Descriptions                             |    |

| 4 Configurations                                  | 14 |

| 4.1 Types of Coprocessors                         | 14 |

| 4.1.1 Single Coprocessor 1                        | 14 |

| 4.1.2 Single Coprocessor 2                        | 14 |

| 4.1.3 Single Coprocessor 1 and 2                  | 15 |

| 4.1.4 Dual Coprocessors using Separate Interfaces |    |

| 4.1.5 No Coprocessors                             | 15 |

| 4.2 Data Transfer Widths                          |    |

| 4.2.1 64-bit Transfer Width                       | 15 |

| 4.2.2 32-bit Transfer Width (Cop2 only)           | 15 |

| 4.3 Out-of-Order Data Transfers                   | 16 |

| 4.4 Multi-Issue Support                           | 16 |

| 4.4.1 Single-Issue Support                        | 16 |

| 4.4.2 Limited Dual-Issue Support                  | 17 |

| 4.4.3 Dual Arithmetic Issues                      | 17 |

| 4.4.4 Additional Multi-Issue Support              | 17 |

| 5 Interface Protocols                             | 18 |

| 5.1 Overview of Transfers                         | 18 |

| 5.2 Instruction Dispatch Transfer                 | 20 |

| 5.3 To Coprocessor Data Transfer                  | 22 |

| 5.4 From Coprocessor Data Transfers               | 22 |

| 5.5 Condition Code Checking                       | 23 |

| 5.6 GPR Data Transfers                            | 23 |

| 5.7 Coprocessor Exceptions                        | 23 |

| 5.8 Instruction Nullification Transfers           | 24 |

| 5.9 Instruction Killing Transfer                  | 25 |

| 5.10 Transfer Example                             | 25 |

| 5.11 Miscellaneous Coprocessor Signals            | 27 |

| 5.11.1 Hardware Present Signaling                 | 27 |

| 5.11.2 Coprocessor Idle                           | 27 |

| 5.11.3 Reset                                      | 27 |

| Appendices                                        |    |

| A Revision History                                |    |

# Core Coprocessor Interface Specification

# **1** Introduction

This document describes the Coprocessor Interface standard supported by various MIPS<sup>TM</sup> processor cores. The Coprocessor Interface is designed to enable coprocessors, such as FPUs and Graphics Engines, to be tightly coupled to an integer processor core. Such coprocessors can be internally developed by MIPS Technologies or externally developed by customers or third party design teams.

*Note:* For clarity, the term *integer processor core* describes the MIPS processor core to which a coprocessor attaches. The integer processor core can do more than integer processing, however. In fact, it can have an internal FPU (and use the Coprocessor Interface for COP2). By the same token, the coprocessor can itself do any kind of processing, including integer calculations.

The Coprocessor Interface has the following features:

- The interface is easy to understand. By keeping the interface as simple as possible, designers can concentrate on the coprocessor's functionality rather than its interface.

- Performance is not compromised. The Coprocessor Interface is compatible with the high-performance features of MIPS microprocessor cores.

- Minimal interface logic is required, which reduces area and power overhead.

- The interface is highly configurable:

- 32-bit or 64-bit data transfers

- COP1 and/or COP2 supported

- From 0 to 7 out-of-order data transfers

- Single issues up to eight issues supported

- A coprocessor built for a low-performance integer processor core can be connected to higher performance integer processor cores. Furthermore, a high-performance coprocessor can be connected to a lower-performance integer processor core.

This document contains the following sections:

- Section 2, "Coprocessor Instructions" describes the specific instructions supported by the Coprocessor Interface.

- Section 3, "Signal Descriptions" describes the signals that make up the interface.

- Section 4, "Configurations" describes the configuration options available with the Coprocessor Interface.

- Section 5, "Interface Protocols" describes the cycle-by-cycle behavior of the signals.

#### 2 Coprocessor Instructions

The Coprocessor Interface supports all coprocessor instructions currently defined in the MIPS32<sup>TM</sup>, MIPS64<sup>TM</sup>, and MIPS-3D<sup>TM</sup> architecture specifications.

These coprocessor instructions are divided into three classes.

- Instructions that perform arithmetic operations (called Arithmetic COP Ops)

- Instructions that move data into the Coprocessor (called To COP Ops)

- Instructions that move data out of the Coprocessor (called *From COP Ops*)

The explicit classification of the opcodes is given below. For a detailed description of these instructions, refer to the MIPS ISA definition or to the Software User's Manual of the appropriate integer processor core.

#### Arithmetic COP Ops:

- COP1 arithmetic instructions (including COP1X and MDMX instructions)

- IR[31:26] = 010001 AND IR[25] = 1

- IR[31:26] = 010011 AND IR[5:4] != 00

- IR[31:26] = 011110

- COP2 arithmetic instructions

- IR[31:26] = 010010 AND IR[25] = 1

- COP1 branch instructions (BC1 instructions)

- IR[31:26] = 010001 AND IR[25:24] = 01

- COP2 branch instructions (BC2 instructions)

- IR[31:26] = 010010 AND IR[25:24] = 01

- Conditional COP1 movement instructions (MOVF, MOVT instructions)

- IR[31:26] = 000000 AND IR[5:0] = 000001

Following COP1 arithmetic instructions test coprocessor condition bits:

• BC1, BC2, MOVF and MOVT (as defined above)

Following COP1 arithmetic instructions test integer processor core registers:

- ALNV.PS

- IR[31:26]=010011 AND IR[5:0]=011110

- ALNV.OB ALNV.QH

- IR[31:26]=011110 AND IR[5:2]=0110 AND IR[0]=1

- MOVN.S MOVZ.S MOVN.D MOVZ.D MOVN.PS MOVZ.PS

- IR[31:26]=010001 AND IR[25:21]=10000 AND IR[5:1]=01001

- IR[31:26]=010001 AND IR[25:21]=10001 AND IR[5:1]=01001

- IR[31:26]=010001 AND IR[25:21]=10110 AND IR[5:1]=01001

For the remainder of this document, the terms 'Arithmetic COP Op' and 'arithmetic instruction' are used interchangeably.

#### From COP Ops:

- COP1 From instructions (including COP1X instructions)

- IR[31:26] = 111001

- IR[31:26] = 111101

- IR[31:26] = 010001 AND IR[25:23] = 000

- IR[31:26] = 010011 AND IR[5:3] = 001 AND IR[2:0] !=111

- COP2 From instructions

- IR[31:26] = 111010

- IR[31:26] = 111110

- IR[31:26] = 010010 AND IR[25:23] = 000

Of the above defined From COP Ops, following are 32-bit instructions

- MFC1, CFC1, SWC1, SWXC1

- IR[31:26] = 010001 AND IR[25:23]=000 AND IR[21]=0

- IR[31:26]=111001

- IR[31:26]= 010011 AND IR[5:0]=001000

- MFHC1 (MIPS32 Release 2 only)

- IR[31:26] = 010001 AND IR[25:21]=00011

- MFC2, CFC2, SWC2

- IR[31:26] = 010010 AND IR[25:23]=000 AND IR[21]=0

- IR[31:26]=111010

- MFHC2 (MIPS32 Release 2 only)

- IR[31:26] = 010010 AND IR[25:21]=00011

Of the above defined From COP Ops, following are 64-bit instructions

- DMFC1, SDC1, SDXC1, SUXC1

- IR[31:26] = 010001 AND IR[25:21]=00001

- IR[31:26]=111101

- IR[31:26]= 010011 AND IR[5:3]=001 AND IR[1:0]=01

- DMFC2, SDC2

- IR[31:26] = 010010 AND IR[25:21]=00001

- IR[31:26]=111110

Remaining instructions are reserved opcodes.

#### To COP Ops:

- COP1 To instructions (including COP1X instructions)

- IR[31:26] = 110001

- IR[31:26] = 110101

- IR[31:26] = 010001 AND IR[25:23] = 001

- IR[31:26] = 010011 AND IR[5:3] = 000

- COP2 To instructions

- IR[31:26] = 110010

- IR[31:26] = 110110

- IR[31:26] = 010010 AND IR[25:23] = 001

Of the above defined To COP Ops, following are 32-bit instructions

- MTC1, CTC1, LWC1, LWXC1

- IR[31:26] = 010001 AND IR[25:23]=001 AND IR[21]=0

- IR[31:26]=110001

- IR[31:26]= 010011 AND IR[5:0]=000000

- MTHC1 (MIPS32 Release 2 only)

- IR[31:26] = 010001 AND IR[25:21]=00111

- MTC2, CTC2, LWC2

- IR[31:26] = 010010 AND IR[25:23]=001 AND IR[21]=0

- IR[31:26]=110010

- MTHC2 (MIPS32 Release 2 only)

- IR[31:26] = 010010 AND IR[25:21]=00111

Of the above defined To COP Ops, following are 64-bit instructions

- DMTC1, LDC1, LDXC1, LUXC1

- IR[31:26] = 010001 AND IR[25:21]=00101

- IR[31:26]=110101

- IR[31:26]= 010011 AND IR[5:3]=000 AND IR[1:0]=01

- DMTC2, LDC2

- IR[31:26] = 010010 AND IR[25:21]=00101

- IR[31:26]=110110

Remaining instructions are reserved opcodes.

### **3** Signal Descriptions

Table 5, Table 6, and Table 7 describe all of the Coprocessor Interface signals. Note that the signals are grouped according to their logical function rather than alphabetically or by their expected physical location. The interactions of signals within these functional groups are described in Section 5, "Interface Protocols".

A separate clock signal is not included in the Coprocessor Interface. All signals are synchronous to the input clock of the integer processor core.

The following tables describe the various attributes of the signals. Table 1 shows the direction of the I/O signal relative to the integer processor core. Table 2 describes how the prefix of a signal determines whether it is required for COP1, COP2, or both. Table 3 and Table 4 describe issue group attributes. For details about the concept of issue groups, see Section 4.4, "Multi-Issue Support" on page 16.

| Dir  | Description                                                                                             |

|------|---------------------------------------------------------------------------------------------------------|

| In   | Input to the integer processor core.                                                                    |

| Out  | Output of the integer processor core.                                                                   |

| SIn  | Static Input to the integer processor core. These signals are normally tied to either power or ground.  |

| SOut | Static Output of the integer processor core. These signals are normally tied to either power or ground. |

#### **Table 1 Signal Direction Key**

#### Table 2 Signal Coprocessor Category

| Prefix | Description                                                                                                                                                                    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CP_    | Required for both COP1 and COP2.<br>Note: These signals may change name to CP1_ or CP2_ when used in certain configurations, refer to sections 4.1.1 through 4.1.4 on page 15. |

| CP1_   | Required for only COP1.                                                                                                                                                        |

| CP2_   | Required only for COP2.                                                                                                                                                        |

#### Table 3 Issue Group Key

| Issue<br>Group | Description                                |

|----------------|--------------------------------------------|

| Comb           | Signal is part of Combined issue groups.   |

| Arith          | Signal is part of Arithmetic issue groups. |

| TF             | Signal is part of To/From issue groups.    |

| NONE           | Signal is not part of any issue groups.    |

#### **Table 4 Signal Issue Group Number**

| Suffix | Description                                                                    |

|--------|--------------------------------------------------------------------------------|

| m      | <i>m</i> determines to which issue group a signal belongs ( $0 \le m \le 7$ ). |

| Table 5 Interface Signal Descriptions | (Required for both COP1 and COP2)   |

|---------------------------------------|-------------------------------------|

| Tuble 5 Interface Signal Descriptions | (Required for both COT I and COT 2) |

| Signal Name             | Dir        | Issue<br>Group        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                 |  |

|-------------------------|------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|

| Instruction Dispatch    |            |                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |  |

| CP_ir_m[31:0]           | Out        | Comb,<br>Arith,<br>TF | <b>Coprocessor Instruction Word.</b> This 32-bit bus contains the coprocessor instruction. It is available in the cycle before <i>CP1_as_m</i> , <i>CP2_as_m</i> , <i>CP1_ts_m</i> , <i>CP2_ts_m</i> , <i>CP1_fs_m</i> , or <i>CP2_fs_m</i> is asserted.                                                                                                                                                                                                                                                       |                                                                                                 |  |

| CP_irenable_m           | Out        | Comb,<br>Arith,<br>TF | <b>Enable Instruction Registering.</b> When this signal is deasserted, no instruction strobes are asserted in the following cycle. When this signal is asserted, there can be an instruction strobe asserted in the following cycle. Instruction strobes include <i>CP1_as_m</i> , <i>CP1_ts_m</i> , <i>CP1_fs_m</i> , <i>CP2_as_m</i> , <i>CP2_ts_m</i> , <i>CP2_fs_m</i> .                                                                                                                                   |                                                                                                 |  |

| CP_order_m[2:0]         | Out        | Comb,<br>Arith,<br>TF | <b>Coprocessor Dispatch Order.</b> This signal signifies the program order of instructions when more than one instruction is issued in a single cycle. Each instruction dispatched has an order value associated with it. There must always be one instruction whose order value is 0. Order values must increment by 1 when more than one instruction is issued in a cycle. This signal is valid when $CP1\_as\_m$ , $CP2\_as\_m$ , $CP1\_ts\_m$ , $CP2\_ts\_m$ , $CP1\_ts\_m$ , or $CP2\_ts\_m$ is asserted. |                                                                                                 |  |

| CP_adisable_m           | SIn        | Comb,<br>Arith        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | patch. When this signal is asserted, the integer ted from dispatching an arithmetic instruction |  |

| CP_tfdisable_m          | SIn        | Comb,<br>TF           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tch. When this signal is asserted, the integer ted from dispatching a To/From instruction       |  |

| CP_inst32_m             | Out        | Comb,<br>Arith,<br>TF | <b>MIPS32 Compatibility Mode</b> – <b>Instructions.</b> When this signal is asserted, the dispatched instruction is restricted to the MIPS32 subset of instructions. Please refer to the <i>MIPS64</i> <sup>TM</sup> <i>Architecture Specification</i> for a complete description of MIPS32 compatibility mode. This signal is valid the cycle before <i>CP1_as_m</i> , <i>CP2_as_m</i> , <i>CP1_fs_m</i> , <i>CP2_fs_m</i> , <i>CP1_ts_m</i> , or <i>CP2_ts_m</i> is asserted.                                |                                                                                                 |  |

| CP_endian_m             | Out        | Comb,<br>Arith,<br>TF | <b>Byte Ordering.</b> When this signal is asserted, the processor is using big-endian byte ordering for the dispatched instruction. When this signal is deasserted, the processor is using little-endian byte ordering. This signal is valid the cycle before <i>CP1_as_m</i> , <i>CP2_as_m</i> , <i>CP1_fs_m</i> , <i>CP2_fs_m</i> , <i>CP1_fs_m</i> , or <i>CP2_fs_m</i> is asserted.                                                                                                                        |                                                                                                 |  |

| To Coprocessor Data (Fo | r all To C | OP Ops)               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |  |

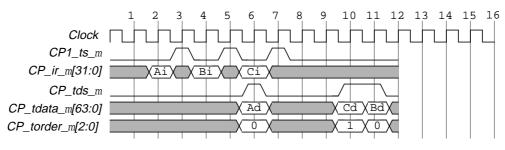

| CP_tds_m                | Out        | Comb,<br>TF           | <b>Coprocessor To Data Strobe.</b> This signal is asserted when To COP Op data is available on <i>CP_tdata_m</i> .                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                 |  |

|                         |            |                       | <b>Coprocessor To Order.</b> This signal specifies for which outstanding To COP Op the data is. This signal is valid only when <i>CP_tds_m</i> is asserted                                                                                                                                                                                                                                                                                                                                                     |                                                                                                 |  |

|                         |            |                       | CP_torder_m[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Order                                                                                           |  |

|                         |            |                       | 3'b000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Oldest outstanding To COP Op data transfer                                                      |  |

|                         |            |                       | 3'b001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2nd oldest To COP Op data transfer                                                              |  |

| CP_torder_m[2:0]        | Out        | Comb,                 | 3'b010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3rd oldest To COP Op data transfer                                                              |  |

|                         |            | TF                    | 3'b011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4th oldest To COP Op data transfer                                                              |  |

|                         |            |                       | 3'b100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5th oldest To COP Op data transfer                                                              |  |

|                         |            |                       | 3'b101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6th oldest To COP Op data transfer                                                              |  |

|                         |            |                       | 3'b110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7th oldest To COP Op data transfer                                                              |  |

|                         | 1          | 1                     | 3'b111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8th oldest To COP Op data transfer                                                              |  |

| Table 5 Interface | Signal Description | s (Required for both    | COP1 and COP2)        |

|-------------------|--------------------|-------------------------|-----------------------|

| Table 5 Interface | bighai Description | s (Inclumental for both | $COTT and COT \Delta$ |

| Signal Name             | Dir         | Issue<br>Group        | Description                                                                                                                                                                                                                                                                                                                                                                 |                          |

|-------------------------|-------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| CP_tordlim_m[2:0]       | SIn         | Comb,<br>TF           | <b>To Coprocessor Data Out-of-Order Limit.</b> This signal forces the integer processor core to limit how much it can reorder To COP Data. The value on this signal corresponds to the maximum allowed value to be used on <i>CP_torder_m[2:0]</i> .                                                                                                                        |                          |

| CP_tdata_m[63:0]        | Out         | Comb,<br>TF           | <b>To Coprocessor Data.</b> Data to be transferred to the coprocessor. For single-word transfers, data is available on <i>CP_tdata_m[31:0]</i> . This bus is valid when <i>CP_tds_m</i> is asserted.<br><i>Note:</i> In 32-bit data transfer size configurations, this bus is reduced to                                                                                    |                          |

| From Commonster Data    | (Fer all F  |                       | <i>CP_tdata_m[31:0]</i> .                                                                                                                                                                                                                                                                                                                                                   |                          |

| From Coprocessor Data   | (For all FI |                       | -                                                                                                                                                                                                                                                                                                                                                                           |                          |

| CP_fds_m                | In          | Comb,<br>TF           | <b>Coprocessor From Data Strobe.</b> This signa<br>COP Op data is available on <i>CP_fdata_m</i> .                                                                                                                                                                                                                                                                          | al is asserted when From |

|                         |             |                       | <b>Coprocessor From Order.</b> This signal spec<br>From COP Op the data is. This signal is vali<br>asserted.                                                                                                                                                                                                                                                                |                          |

|                         |             |                       | CP_forder_m 0                                                                                                                                                                                                                                                                                                                                                               | rder                     |

|                         |             |                       | 3'b000 Oldest outstanding Fro                                                                                                                                                                                                                                                                                                                                               | om COP Op data transfer  |

|                         |             |                       | 3'b001 2nd oldest From COP                                                                                                                                                                                                                                                                                                                                                  | Op data transfer         |

| CP_forder_m[2:0]        | In          | Comb,<br>TF           | 3'b010 3rd oldest From COP                                                                                                                                                                                                                                                                                                                                                  | Op data transfer         |

|                         |             |                       | 3'b011 4th oldest From COP                                                                                                                                                                                                                                                                                                                                                  | Op data transfer         |

|                         |             |                       | 3'b100 5th oldest From COP                                                                                                                                                                                                                                                                                                                                                  | Op data transfer         |

|                         |             |                       | 3'b101 6th oldest From COP                                                                                                                                                                                                                                                                                                                                                  | Op data transfer         |

|                         |             |                       | 3'b110 7th oldest From COP                                                                                                                                                                                                                                                                                                                                                  | Op data transfer         |

|                         |             |                       | 3'b111 8th oldest From COP                                                                                                                                                                                                                                                                                                                                                  | Op data transfer         |

| CP_fordlim_m[2:0]       | SOut        | Comb,<br>TF           |                                                                                                                                                                                                                                                                                                                                                                             |                          |

| CP_fdata_m[63:0]        | In          | Comb,<br>TF           | <ul> <li>From Coprocessor Data. This 64-bit bus contains data to be transferred from coprocessor. For single-word transfers, data must be duplicated on both <i>CP_fdata_m[63:32]</i> and <i>CP_fdata_m[31:0]</i>. This bus is valid when <i>CP_fds_m</i> is asserted.</li> <li><i>Note:</i> In 32-bit data transfer size configurations, this bus is reduced to</li> </ul> |                          |

|                         |             |                       | <i>CP_fdata_m[31:0]</i> .                                                                                                                                                                                                                                                                                                                                                   |                          |

| Coprocessor Condition C | ode Chec    | k (Only for           | BC1, MOVF, MOVT, BC2 Ops)                                                                                                                                                                                                                                                                                                                                                   |                          |

| CP_cccs_m               | In          | Comb,<br>Arith        | Coprocessor Condition Code Check Strol<br>when condition code check results are available                                                                                                                                                                                                                                                                                   |                          |

| CP_ccc_m                | In          | Comb,<br>Arith        | <b>Coprocessor Condition Code Check.</b> This signal is valid when <i>CP_cccs_m</i> is asserted. When this signal is asserted, the instruction checking the condition code should proceed with its execution (branch or move data). When this signal is deasserted, the instruction should not execute its conditional operation (do not branch and do not move data).      |                          |

| Coprocessor Exceptions  |             |                       |                                                                                                                                                                                                                                                                                                                                                                             |                          |

| CP_excs_m               | In          | Comb,<br>Arith,<br>TF | <b>Coprocessor Exception Strobe.</b> This signal is asserted when coprocessor exception signalling is available on <i>CP_exc_m</i> .                                                                                                                                                                                                                                        |                          |

| Signal Name               | Dir | Issue<br>Group        |                                                                                                                                                                                                                                                                                                                            | Description                                                                                              |

|---------------------------|-----|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| CP_exc_m                  | In  | Comb,<br>Arith,<br>TF | <b>Coprocessor Exception.</b> When this signal is deasserted, the coprocessor is not causing an exception. When this signal is asserted, the coprocessor is causing an exception. The type of exception is encoded on the signal <i>CP_exccode_m[4:0]</i> . This signal is valid when <i>CP_excs_m</i> is asserted.        |                                                                                                          |

|                           |     |                       | Coprocessor Exception<br>asserted and CP_exc_m                                                                                                                                                                                                                                                                             | <b>Code.</b> This signal is valid when <i>CP_excs_mis</i> is asserted.                                   |

|                           |     |                       | CP_exccode_m[4:0]                                                                                                                                                                                                                                                                                                          | Exception                                                                                                |

|                           |     |                       | 5'b01010                                                                                                                                                                                                                                                                                                                   | Reserved Instruction Exception                                                                           |

|                           |     | Comb,                 | 5'b01111                                                                                                                                                                                                                                                                                                                   | Floating-Point Exception                                                                                 |

| CP_exccode_m[4:0]         | In  | Arith,                | 5'b10000                                                                                                                                                                                                                                                                                                                   | Available for implementation-specific use                                                                |

|                           |     | TF                    | 5'b10010                                                                                                                                                                                                                                                                                                                   | COP2 Exception                                                                                           |

|                           |     |                       |                                                                                                                                                                                                                                                                                                                            | Reserved.                                                                                                |

|                           |     |                       | other values                                                                                                                                                                                                                                                                                                               | If other values are signalled, the operation of the integer processor core is UNDEFINED.                 |

| Instruction Nullification |     |                       |                                                                                                                                                                                                                                                                                                                            |                                                                                                          |

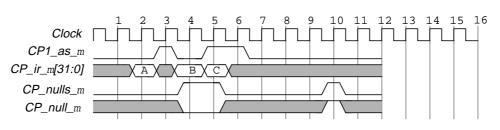

| CP_nulls_m                | Out | Comb,<br>Arith,<br>TF | <b>Coprocessor Null Strobe.</b> This signal is asserted when a nullification signal is available on <i>CP_null_m</i> .                                                                                                                                                                                                     |                                                                                                          |

| CP_null_m                 | Out | Comb,<br>Arith,<br>TF | <b>Nullify Coprocessor Instruction.</b> When this signal is deasserted, the integer processor core is signalling that the instruction is not nullified. When this signal is asserted, the integer processor core is signalling that the instruction is nullified. This signal is valid when <i>CP_nulls_m</i> is asserted. |                                                                                                          |

| Instruction Killing       |     |                       |                                                                                                                                                                                                                                                                                                                            |                                                                                                          |

| CP_kills_m                | Out | Comb,<br>Arith,<br>TF | <b>Coprocessor Kill Strobe.</b> This signal is asserted when kill signalling is available on <i>CP_kill_m</i> .                                                                                                                                                                                                            |                                                                                                          |

|                           |     |                       |                                                                                                                                                                                                                                                                                                                            | uction. This signal indicates whether or not a is killed. It is valid when <i>CP_kills_m</i> is asserted |

|                           |     |                       | CP_kill_m[1:0]                                                                                                                                                                                                                                                                                                             | / Type of Kill                                                                                           |

|                           |     | Comb,                 | 2'b00                                                                                                                                                                                                                                                                                                                      | Instruction is not killed and can commit                                                                 |

| CP_kill_m[1:0]            | Out | Arith,<br>TF          | 2'b01                                                                                                                                                                                                                                                                                                                      | its results                                                                                              |

|                           |     |                       | 2'b10                                                                                                                                                                                                                                                                                                                      | Instruction is killed (not due to<br><i>CP_exc_m</i> )                                                   |

|                           |     |                       | 2'b11                                                                                                                                                                                                                                                                                                                      | Instruction is killed (due to <i>CP_exc_m</i> )                                                          |

| Miscellaneous             |     | I                     | I                                                                                                                                                                                                                                                                                                                          |                                                                                                          |

| CP_reset                  | Out | NONE                  |                                                                                                                                                                                                                                                                                                                            | is signal is asserted when the integer processor<br>soft reset. At a minimum, this signal is asserted    |

| CP_idle                   | In  | NONE                  | <b>Coprocessor Idle.</b> This signal is asserted when the coprocessor logic is idle. It enables the integer processor core to go into sleep mode and shut down the internal integer processor core clock. This signal is valid only if <i>CP1_fppresent</i> , <i>CP1_ndmxpresent</i> , or <i>CP2_present</i> is asserted.  |                                                                                                          |

# Table 5 Interface Signal Descriptions (Required for both COP1 and COP2)

|                      |        | Issue                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|----------------------|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal Name          | Dir    | Group                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Instruction Dispatch |        |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

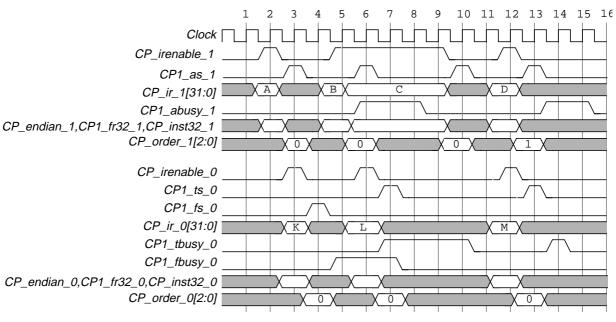

| CP1_as_m             | Out    | Comb,<br>Arith        | <b>Coprocessor 1 Arithmetic Instruction Strobe.</b> This signal is asserted in the cycle after an Arithmetic COP1 Op instruction is available on <i>CP_ir_m</i> . If <i>CP1_abusy_m</i> was asserted in the previous cycle, this signal is not asserted. In any cycle, at most one of the following signals can be asserted at a time in a particular issue group: <i>CP1_as_m</i> , <i>CP2_as_m</i> , <i>CP1_ts_m</i> , <i>CP2_ts_m</i> , <i>CP1_fs_m</i> , <i>CP2_fs_m</i> . |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| CP1_abusy_m          | In     | Comb,<br>Arith        | arithmetic instruction is no                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>Coprocessor 1 Arithmetic Busy.</b> When this signal is asserted, a Coprocessor 1 arithmetic instruction is not dispatched. <i>CP1_as_m</i> is not asserted in the cycle after this signal is asserted.                                                                                                                                                                                                                                                   |  |  |

| CP1_ts_m             | Out    | Comb,<br>TF           | Op instruction is available<br>previous cycle, this signal<br>signals can be asserted at                                                                                                                                                                                                                                                                                                                                                                                       | <b>Coprocessor 1 To Strobe.</b> This signal is asserted in the cycle after a To COP1<br>Op instruction is available on <i>CP_ir_m</i> . If <i>CP1_tbusy_m</i> was asserted in the<br>previous cycle, this signal is not asserted. In any cycle, at most 1 of the following<br>signals can be asserted at a time in a particular issue group: <i>CP1_as_m</i> ,<br><i>CP2_as_m</i> , <i>CP1_ts_m</i> , <i>CP2_ts_m</i> , <i>CP1_fs_m</i> , <i>CP2_fs_m</i> . |  |  |

| CP1_tbusy_m          | In     | Comb,<br>TF           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | When this signal is asserted, a To COP1 Op is not not asserted in the cycle after this signal is asserted.                                                                                                                                                                                                                                                                                                                                                  |  |  |

| CP1_fs_m             | Out    | Comb,<br>TF           | COP1 Op instruction is av<br>the previous cycle, this sig<br>following signals can be a                                                                                                                                                                                                                                                                                                                                                                                        | <b>Coprocessor 1 From Strobe.</b> This signal is asserted in the cycle after a From COP1 Op instruction is available on <i>CP_ir_m</i> . If <i>CP1_fbusy_m</i> was asserted in the previous cycle, this signal is not asserted. In any cycle, at most one of the following signals can be asserted at a time in a particular issue group:<br><i>CP1_as_m</i> , <i>CP2_as_m</i> , <i>CP1_ts_m</i> , <i>CP2_ts_m</i> , <i>CP1_fs_m</i> , <i>CP2_fs_m</i> .    |  |  |

| CP1_fbusy_m          | In     | Comb,<br>TF           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>From Coprocessor 1 Busy.</b> When this signal is asserted, a From COP1 Op is not dispatched. <i>CP1_fs_m</i> is not asserted in the cycle after this signal is asserted.                                                                                                                                                                                                                                                                                 |  |  |

| <i>CP1_fr32_</i> m   | Out    | Comb,<br>Arith,<br>TF | <b>MIPS32-Compatibility Mode – Registers.</b> When this signal is asserted, the dispatched instruction uses the MIPS32-compatible register file. This signal is valid the cycle before <i>CP1_as_m</i> , <i>CP1_fs_m</i> , or <i>CP1_ts_m</i> is asserted.                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| GPR Data (Only for A | LNV.PS | , ALNV.fm             | t, MOVN.fmt, MOVZ.fmt                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Arithmetic COP1 Ops)                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| CP1_gprs_m           | Out    | Comb,<br>Arith        | GPR Strobe. This signal information is available or                                                                                                                                                                                                                                                                                                                                                                                                                            | is asserted when additional general-purpose register a <i>CP1_gpr_m</i> .                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                      |        |                       | register file. CP1_gpr_m[2<br>ALNV.PS and ALNV.fmt                                                                                                                                                                                                                                                                                                                                                                                                                             | lies additional data from the integer general-purpose<br><i>c:0]</i> is valid when <i>CP1_gprs_m</i> is asserted and only fo<br>instructions. <i>CP1_gpr_m[3]</i> is valid when<br>and only for MOVN.fmt and MOVZ.fmt instructions.                                                                                                                                                                                                                         |  |  |

|                      |        |                       | CP1_gpr_m[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RS<br>(Valid only for ALNV.PS, ALNV.fmt)                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| CP1_gpr_m[3:0]       | Out    | Comb,<br>Arith        | Binary encoded                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Lower 3 bits of RS register contents                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                      |        |                       | CP1_gpr_m[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RT Zero Check<br>(Valid only for MOVN.fmt, MOVZ.fmt)                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                      |        |                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RT!= 0                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                      |        |                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RT==0                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Miscellaneous        |        | <u> </u>              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| CP1_fppresent        | SIn    | NONE                  | <b>COP1 FPU Present.</b> This connected to the Coproces                                                                                                                                                                                                                                                                                                                                                                                                                        | signal must be asserted when COP1 FPU hardware i ssor Interface.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| CP1_mdmxpresent      | SIn    | NONE                  | <b>COP1 MDMX Present.</b> This signal must be asserted when COP1 MDMX hardware is connected to the Coprocessor Interface.                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

Table 6 Coprocessor Interface Signal Descriptions (Required only for COP1)

| Signal Name        | Dir | Issue<br>Group        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|--------------------|-----|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

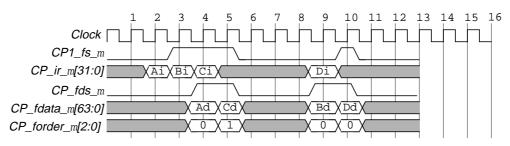

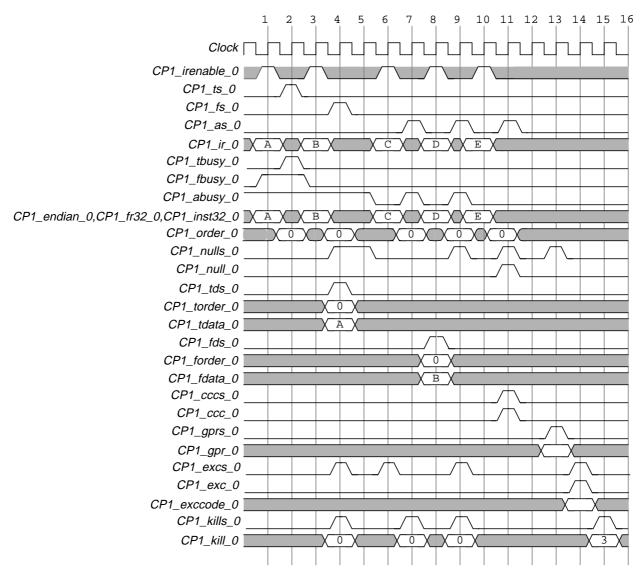

|                    |     | Group                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |